晶体谐振器就是指用石英材料做成的石英晶体谐振器,俗称晶振;起产生频率的作用,具有稳定,抗干扰性能良好的特点,广泛应用于各种电子产品中。

1、标称频率

指晶体元件规范中所指定的频率,即振荡器输出的中心频率或频率的标称值。

2、调整频差

在指定温度范围内,振荡器输出频率相对于25℃时测量值的zui大允许频率偏差,常用 ppm(1/106)表示。

3、温度频差

在标称电源和负载下,工作在规定温度范围内的不带隐含基准温度或带隐含基准温度的zui大允许频偏。常用 ppm(1/106)表示。

4、工作温度范围

能够保证振荡器输出频率及其化各种特性符合指标的温度范围。

5、老化率

指在恒定的环境条件下测量振荡器频率时,振荡器频率和时间之间的关系。这种长期频率漂移是由石英晶体元件和贴片振荡器电路元件的缓慢变化造成的,因此,其频率偏移的速率叫老化率。

6、谐振电阻(Rr)

指晶体元件在谐振频率处的等效电阻,当不考虑 C0 的作用,也近似等于所谓晶体的动态电阻 R1 或称等效串联电阻(ESR)。这个参数控制着晶体元件的品质因数,还决定所应用电路中的晶体振荡电平,因而影响晶体的稳定性以致是否可以理想的起振。所以它是晶体元件的一个重要指标参数。一般的,对于一给定频率,选用的晶体盒越小,ESR 的平均值可能就越高;绝大多数情况,在制造过程中并不能预计具体某个晶体元件的电阻值,而只能保证电阻将低于规范中所给的zui大值。

7、负载谐振电阻(RL)

指晶体元件与规定外部电容相串联,在负载谐振频率 FL 时的电阻。对一给定晶体元体,其负载谐振电阻值取决于和该元件一起工作的负载电容值,串上负载电容后的谐振电阻,总是大于晶体元件本身的谐振电阻。

8、负载电容(CL)

与晶体元件一起决定负载谐振频率 FL 的有效外界电容。晶体元件规范中的 CL 是一个测试条件也是一个使用条件,这个值可在用户具体使用时根据情况作适当调整,来微调 FL 的实际工作频率(也即晶体的制造公差可调整)。但它有一个合适值,否则会给振荡电路带来恶化,其值通常采用 10pF、15pF 、20pF、30pF、50pF、∝等,其中当 CL 标为∝时表示其应用在串联谐振型电路中,不要再加负载电容,并且工作频率就是晶体的(串联)谐振频率 Fr。用户应当注意,对于某些晶体(包括不封装的振子应用),在某一生产规范既定的负载电容下(特别是小负载电容时),±0.5pF 的电路实际电容的偏差就能产生±10×10-6 的频率误差。因此,负载电容是一个非常重要的订货规范指标。

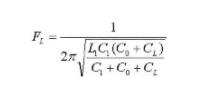

9、谐振频率(Fr)

指在规定条件下,晶体元件电气阻抗为电阻性的两个频率中较低的一个频率。根据等效电路,当不考虑 C0 的作用,Fr 由 C1 和 L1 决定,近似等于所谓串联(支路)谐振频率(Fs)。这一频率是晶体的自然谐振频率,它在高稳晶振的设计中,是作为使晶振稳定工作于标称频率、确定频率调整范围、设置频率微调装置等要求时的设计参数。

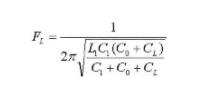

10、负载谐振频率(FL)

指在规定条件下,晶体元件与一负载电容串联或并联,其组合阻抗呈现为电阻性时两个频率中的一个频率。在串联负载电容时,FL 是两个频率中较低的那个频率;在并联负载电容时,FL 则是其中较高的那个频率。对于某一给定的负载电容值(CL),就实际效果,这两个频率是相同的;而且这一频率是晶体的绝大多数应用时,在电路中所表现的实际频率,也是制造厂商为满足用户对产品符合标称频率要求的测试指标参数。

11、品质因数(Q)

品质因数又称机械 Q 值,它是反映谐振器性能好坏的重要参数,它与 L1 和 C1 有如下关系:

Q=wL1/R1=1/wR1C1

如上式,R1 越大,Q 值越低,功率耗散越大,而且还会导致频率不稳定。反之 Q 值越高,频率越稳定。

12、激励电平(Level of drive)

是一种用耗散功率表示的,施加于晶体元件的激励条件的量度。所有晶体元件的频率和电阻都在一定程度上随激励电平的变化而变化,这称为激励电平相关性(DLD),正因为晶体元件固有的激励电平相关性的特性,用户在振荡电路设计和晶体使用时,必须注意和保证不出现激励电平过低而起振不良或过度激励频率异常的现象。